## Features

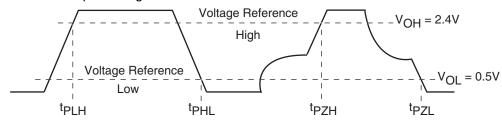

- 16-/32-bit Data and Address Register

- 16-Mbyte Direct Addressing Range

- 56 Powerful Instruction Types

- Operations on Five Main Data Types

- Memory Mapped Input/Output

- 14 Addressing Modes

- Three Available Versions: 8 MHz/10 MHz and 12.5 MHz

- Military Temperature Range: -55/+125°C

- Power Supply: 5V<sub>DC</sub> ± 10%

# Description

The TS68C000 reduced power consumption device dissipates an order of magnitude less power than the HMOS TS68000. The TS68C000 is an implementation of the TS68000 16/32 microprocessor architecture. The TS68C000 has a 16-bit data bus and 24-bit address bus while the full architecture provides for 32-bit address and databuses. It is completely code-compatible with the HMOS TS68000, TS68008 8-bit data bus implementation of the TS68000 and the TS68020 32-bit implementation of the architecture. Any user-mode programs written using the TS68C000 instruction set will run unchanged on the TS68000, TS68008 and TS68020. This is possible because the user programming model is identical for all processors and the instruction sets are proper sub-sets of the complete architecture.

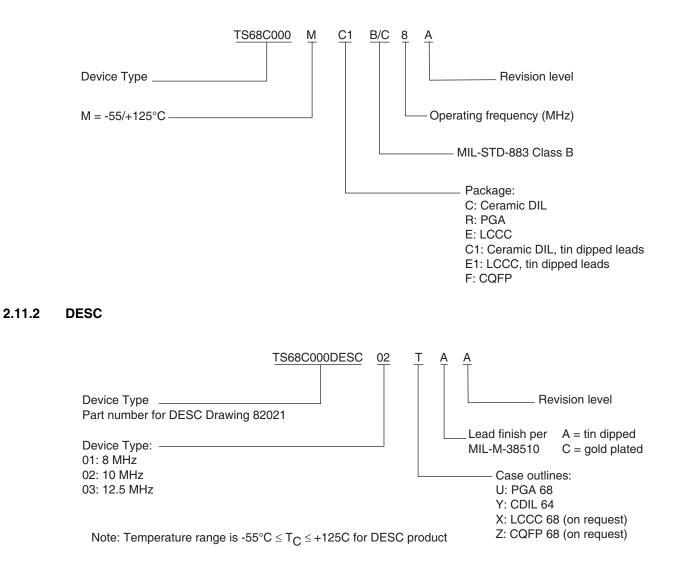

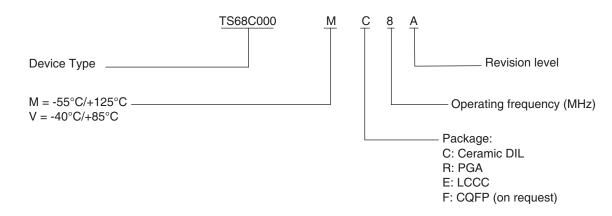

## Screening/Quality

This product is manufactured in full compliance with:

- MIL-STD-883 class B

- DESC drawing 5962-89462

- Atmel standards

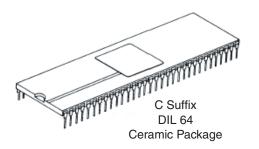

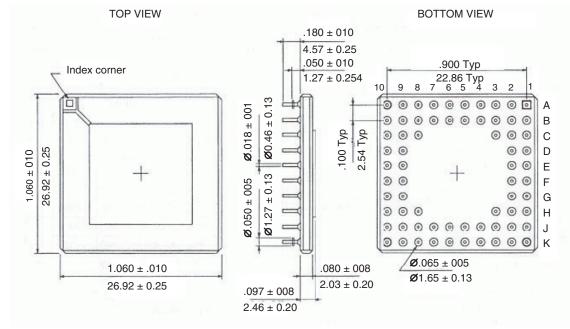

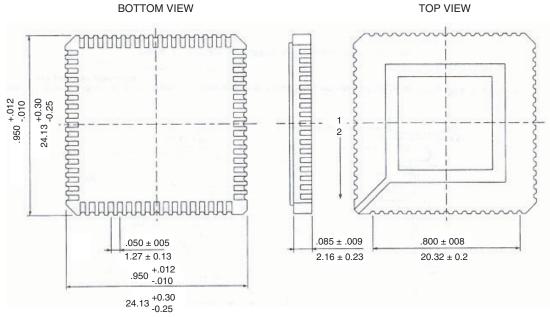

E Suffix LCCC 68 Leadless Ceramic Chip Carrier

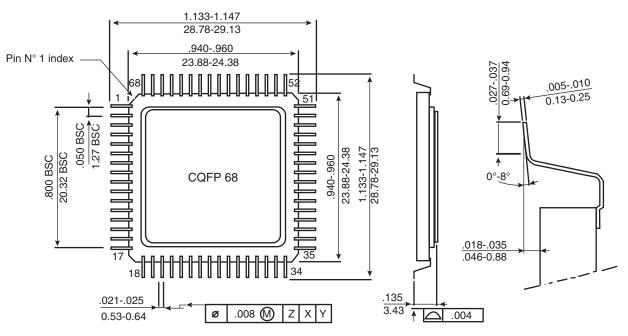

F Suffix CQFP 68 Ceramic Quad Flat Pack (on request)

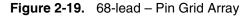

R Suffix PGA 68 Pin Grid Array

Low Power HCMOS 16-/32-bit Hi-Rel Microprocessor

# TS68C000

Rev. 2170A-HIREL-09/05

## 1. General Description

## 1.1 Introduction

This detail specification contains both a summary of the TS68C000 as well as detailed set of parametrics. The purpose is twofold to provide an instruction to the TS68C000 and support for the sophisticated user. For detail information on the TS68C000, refer to "68000 16-bit microprocessor user's manual".

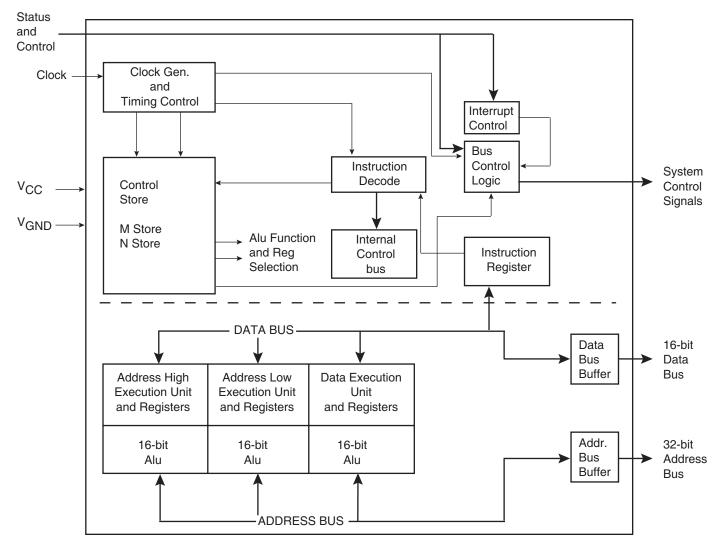

## 1.2 Detailed Block Diagram

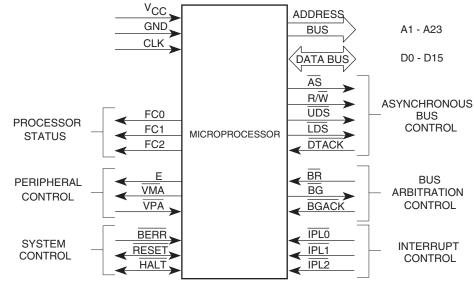

The functional block diagram is given in Figure 1-1 below.

Figure 1-1. Block Diagram

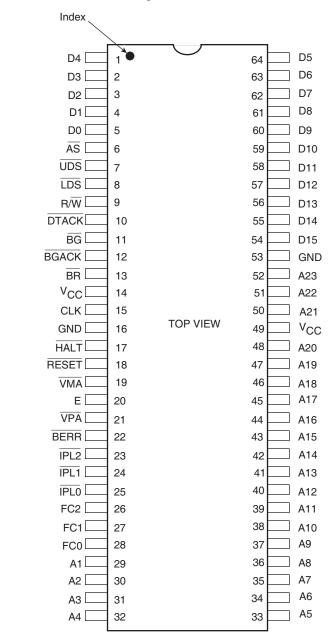

## 1.3 Pin Assignments

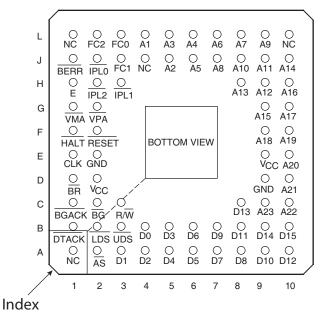

Figure 1-2. 64-lead Dual-in-Line Package

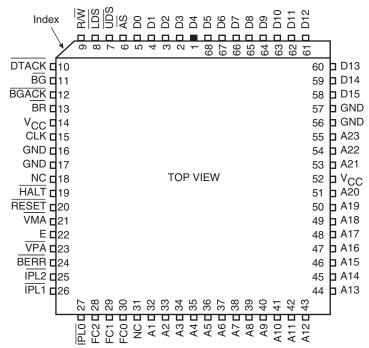

#### Figure 1-3. 68-terminal Pin Grid Array

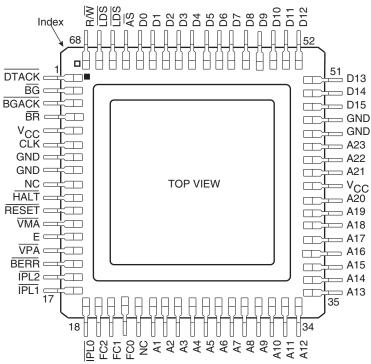

#### Figure 1-4. 68-lead Quad Pack

# TC68C000

4

#### Figure 1-5. 68-ceramic Quad Flat Pack

## 1.4 Terminal Designations

The function, category and relevant symbol of each terminal of the device are given in the following table.

| Symbol                         | Function                   | Category  |

|--------------------------------|----------------------------|-----------|

| V <sub>CC</sub>                | Power supply (2 terminals) | Supply    |

| V <sub>SS</sub> <sup>(1)</sup> | Power supply (2 terminals) | Terminals |

| FC0 to FC2                     | Processor status           | Outputs   |

| IPL0 to IPL2                   | Interrupt control          | Inputs    |

| A1 to A23                      | Address bus                | Outputs   |

| AS                             |                            |           |

| R/W                            |                            | Outeute   |

| UDS                            | Asynchronous bus control   | Outputs   |

| LDS                            |                            |           |

| DTACK                          | -                          | Input     |

| BR                             |                            | Innuto    |

| BGACK                          | Bus arbitration control    | Inputs    |

| BG                             |                            | Output    |

Table 1-1.Terminal Designations

| Table 1-1. | Terminal Designations (Cor | tinued) |

|------------|----------------------------|---------|

|------------|----------------------------|---------|

| Symbol    | Function                | Category     |

|-----------|-------------------------|--------------|

| BERR      |                         | Input        |

| RESET     | System control          | Input/Output |

| HALT      |                         | Input/Output |

| VPA       |                         | Input        |

| VMA       | 6800 peripheral control | Output       |

| E         |                         | Output       |

| CLK       | Clock                   | Input        |

| D0 to D15 | Data bus                | Input/Output |

Note: 1.  $V_{SS}$  is the reference terminal for the voltages

## 1.5 Signal Description

The input and output signals are illustrated functionally in Figure 1-6 and are described in the following paragraphs.

Figure 1-6. Input and Output Signals

Table 1-2.

Data Strobe Control of Data Bus

| UDS  | LDS  | R/W  | D8-D15               | D0-D7                |

|------|------|------|----------------------|----------------------|

| High | High |      | No valid data        | No valid data        |

| Low  | Low  | High | Valid data bits 8-15 | Valid data bits 0-7  |

| High | Low  | High | No valid data        | Valid data bits 0-7  |

| Low  | High | High | Valid data bits 8-15 | No valid data        |

| Low  | Low  | Low  | Valid data bits 8-15 | Valid data bits 0-7  |

| High | Low  | Low  | Valid data bits 0-7  | Valid data bits 0-7  |

| Low  | High | High | Valid data bits 8-15 | Valid data bits 8-15 |

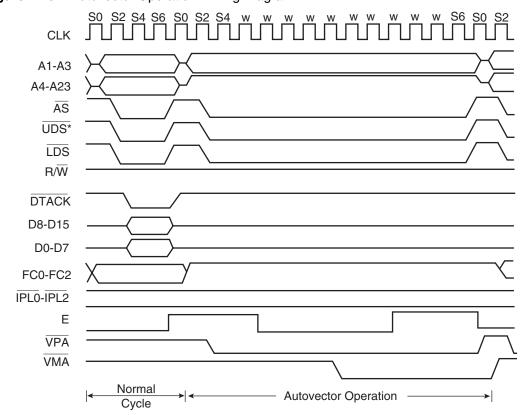

1.5.0.1 Address Bus (A1 through A23)

This 24-bit, unidirectional, three-state bus is capable of addressing 16 megabytes of data. It provides the address for bus operation during all cycles except interrupt cycles. During interrupt cycles, address lines A1, A2 and A3 provide information about what level interrupt is being serviced while address lines A4 through A23 are set to a logic high.

#### 1.5.0.2 Data Bus (D0 Through D15)

This 16-bit, bidirectional, three-state bus is the general-purpose data path. It can transfer and accept data in either word or byte length. During an interrupt acknowledge cycle, the external device supplies the vector number on data lines D0-07.

#### 1.5.0.3 Asynchronous Bus Control

Asynchronous data transfers are handled using the following control signals: address strobe, read/write, upper and lower data strobes, and data transfer acknowledge. These signals are explained in the following paragraphs.

#### ADDRESS STROBE (AS)

This signal indicates that there is a valid address on the address bus.

#### READ/WRITE (R/W)

This signal defines the data bus transfer as a read or write cycle. The R/W signal also works in conjunction with the data strobes as explained in the following paragraph.

#### UPPER AND LOWER DATA STROBE (UDS, LDS)

These signals control the flow of data on the data bus, as shown in Table 1-2. When the  $R/\overline{W}$  line is high, the processor will read from the data bus as indicated. When the R/W line is low, the processor will write to the data bus as shown.

#### DATA TRANSFER ACKNOWLEDGE (DTACK)

This input indicates that the data transfer is completed. When the processor recognizes DTACK during a read cycle, data is latched and the bus cycle terminated. When DTACK is recognized during a write cycle, the bus cycle is terminated.

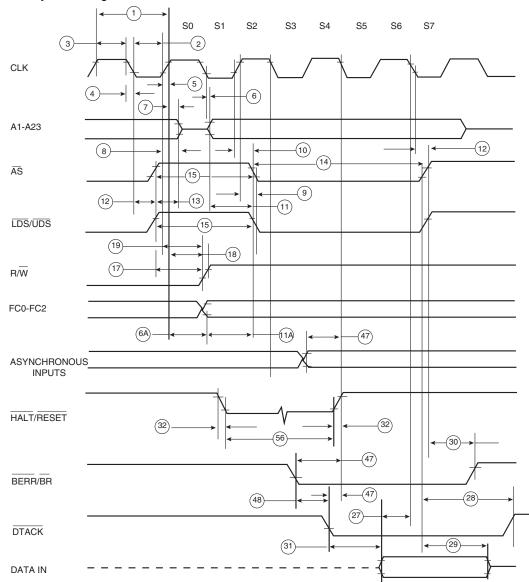

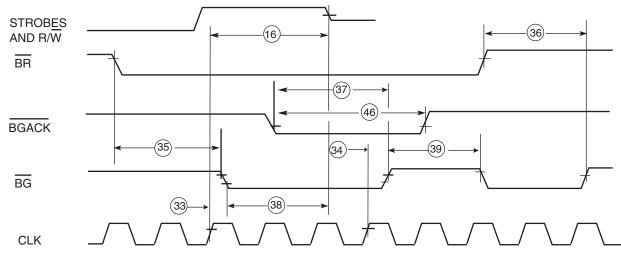

#### 1.5.0.4 Bus Arbitration Control

The three signals, bus request, bus grant, and bus grant acknowledge, form a bus arbitration circuit to determine which device will be the bus master device.

#### BUS REQUEST (BR)

This input is wire ORed with all other devices that could be bus masters. This input indicates to the processor that some other device desires to become the bus master.

#### BUS GRANT (BG)

This output indicates to all other potential bus master devices that the processor will release bus control at the end of the current bus cycle.

#### BUS GRANT ACKNOWLEDGE (BGACK)

This input indicates that some other device has become the bus master.

This signal should not be asserted until the following four conditions are met:

- 1. a bus grant has been received,

- 2. address strobe is inactive which indicates that the microprocessor is not using the bus,

- 3. data transfer acknowledge is Inactive which indicates that neither memory nor peripherals are using the bus, and

- 4. bus grant acknowledge is inactive which indicates that no other device is still claiming bus mastership.

#### 1.5.0.5 Interrupt Control (IPL0, IPL1, IPL2)

These Input pins indicate the encoded priority level of the device requesting an interrupt. Level seven is the highest priority white level zero indicates that no interrupts are requested. Level seven cannot be masked. The least significant bit is given in IPLO and the most significant bit is contained in IPL2. These lines must remain stable until the processor signals interrupt acknowledge (FC0-FC2 are all high) to insure that the interrupt is recognized.

#### 1.5.0.6 System Control

The system control inputs are used to either reset or halt the processor and to indicate to the processor that bus errors have occurred. The three system control inputs are explained in the following paragraphs.

#### BUS ERROR (BERR)

This input informs the processor that there is a problem with the cycle currently being executed. Problems may be a result of:

- 1. nonresponding devices,

- 2. interrupt vector number acquisition failure,

- 3. illegal access request as determined by a memory management unit, or

- 4. other application dependent errors.

The bus error signal interacts with the halt signal to determine if the current bus cycle should be re-executed or if exception processing should be performed.

#### RESET (RESET)

This bidirectional signal line acts to reset (start a system initialization sequence) to processor in response to an external reset signal. An internally generated reset (result of a RESET instruction) causes all external devices to be reset and the internal of the processor is not affected. A total system reset (processor and external devices) is the result of external HALT and RESET signals applied at the same time.

#### HALT (HALT)

When this bldirectional line is driven by an external device, it will cause the processor to stop at the completion of the current bus cycle. When the processor has been halted using this input, all control signals are inactive and all three-state lines are put in their high-impedance state.

When the processor has stopped executing Instructions, such as in a double bus fault condition, the  $\overline{\text{HALT}}$  line is driven by the processor to indicate to external devices that the processor has stopped.

8

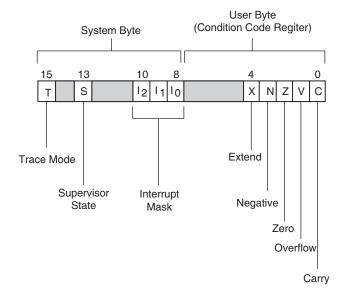

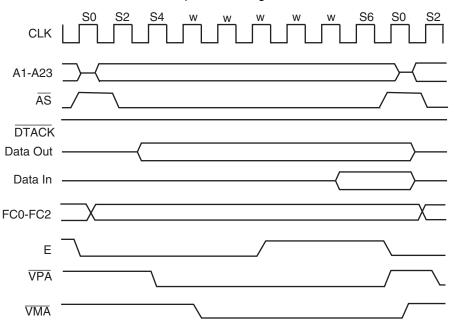

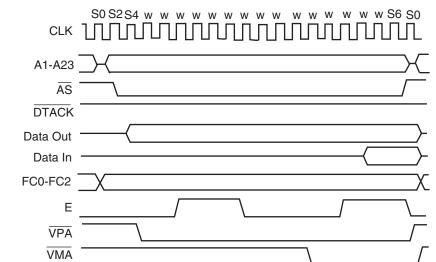

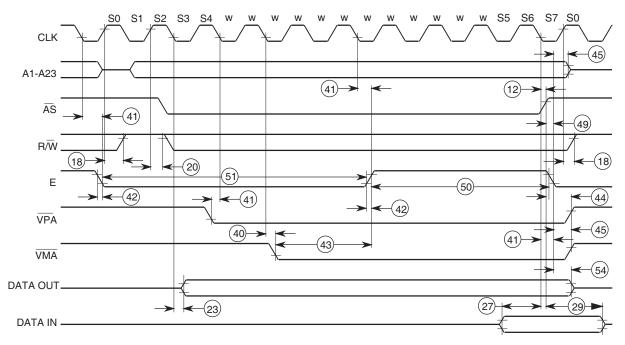

#### 1.5.0.7 EF 6800 Peripheral Control

These control signals are used to allow the interfacing of synchronous EF 6800 peripheral devices with the asynchronous TS68C000. These signals are explained in the following paragraphs.

#### ENABLE (E)

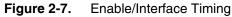

This signal is the standard enable signal common to all EF 6800 type peripheral devices. The period for this output is ten TS68C000 clock periods (six clocks low, four clocks high). Enable is generated by an internal ring counter which may come up in any state (i.e., at power on, it is impossible to guarantee phase relationship of E to CLK). E is a free-running crack and runs regardless of the state of the bus on the MPU.

#### VALID PERIPHERAL ADDRESS (VPA)

This input indicates that the device or region addressed is an TS68000 Family device and that data transfer should be synchronized with the enable (E) signal. This Input also indicates that the processor should use automatic vectoring for an interrupt during an IACK cycle.

#### VALID MEMORY ADDRESS (VMA)

This output is used to indicate to TS68000 peripheral devices that there is a valid address on the address bus and the processor is synchronized to enable. This signal only responds to a valid peripheral address (VPA) input which indicates that the peripheral is an TS68000 Family device.

#### 1.5.0.8 Processor Status (FC0, FC1, FC2)

These function code outputs indicate the state (user or supervisor) and the cycle type currently being executed, as shown in Table 1-3. The information indicated by the function code outputs is valid whenever address strobe  $(\overline{AS})$  is active.

| Table 1-3. | Processor Status T | able |                       |  |

|------------|--------------------|------|-----------------------|--|

|            | Function Code Outp | but  |                       |  |

| FC2        | FC1                | FC0  | Cycle Time            |  |

| Low        | Low                | Low  | (Undefined, reserved) |  |

| Low        | Low                | High | User data             |  |

| Low        | High               | Low  | User program          |  |

| Low        | High               | High | (Undefined, reserved) |  |

| High       | Low                | Low  | (Undefined, reserved) |  |

| High       | Low                | High | Supervisor data       |  |

| High       | High               | Low  | Supervisor program    |  |

| High       | High               | High | Interrupt acknowledge |  |

Table 1-3. Processor Status Table

#### 1.5.0.9 Clock (CLK)

The clock input is a TTL-compatible signal that is internally buffered for development of the internal clocks needed by the processor. The clock input should not be gated off at any time and the clock signal must conform to minimum and maximum pulse width times. The clock is a constant frequency square wave with no stretching or shaping techniques required.

## 2. Detailed Specifications

## 2.1 Scope

This drawing describes the specific requirements for the microprocessor TS68C000, 8 MHz, 10 MHz and 12.5 MHz, in compliance with MIL-STD-883 class B.

### 2.2 Applicable Documents

#### 2.2.1 MIL-STD-883

- 1. MIL-STD-883: Test Methods and Procedures For Electronics

- 2. MIL-PRF-38535 Appendix A: General Specifications for Microcircuits

#### 2.3 Requirements

#### 2.3.1 General

The microcircuits are in accordance with the applicable document and as specified herein.

### 2.4 Design and Construction

#### 2.4.1 Terminal Connections

Depending on the package, the terminal connections shall be as shown in Figure 1-2, Figure 1-3, Figure 1-4 and Figure 1-5.

#### 2.4.2 Lead Material and Finish

Lead material and finish shall be any option of MIL-PRF-38535 Appendix A-3-5-6 "Package Element Material and Finsh".

#### 2.4.3 Package

The macrocircuits are packaged in hermetically sealed ceramic package which is conform to case outlines of MIL-PRF-38535 Appendix A-3-5-1.

- PGA68 64 LEAD DIP

- 64 DILSQ. LCC 68 PINS

- 68 LCCC68 TERMINALS JCC

- 68 CQFP

The precise case outlines are described on figures and into MIL-M-38510.

#### 2.4.4 Electrical Characteristics

#### 2.4.4.1 Absolute Maximum Ratings

Limiting conditions (ratings) defined below shall not be for inspection purposes. However some limiting conditions (ratings) may be taken in other parts of this specification as detail conditions for an applicable test.

Unless otherwise stated, all voltages are referenced to the reference terminal as defined in Table 1-1, "Terminal Designations" on page 5 of this specification.

| Symbol             | Parameter             | Test Conditions            | Min  | Max  | Unit |

|--------------------|-----------------------|----------------------------|------|------|------|

| V <sub>cc</sub>    | Supply voltage        |                            | -0.3 | +6.5 | V    |

| VI                 | Input voltage         |                            | -0.3 | +6.5 | V    |

| Vo                 | Output voltage        |                            | NA   | NA   | V    |

| V <sub>oz</sub>    | Off state voltage     |                            | -0.3 | 11.0 | V    |

| Ι <sub>ο</sub>     | Output currents       |                            | NA   | NA   | mA   |

| l <sub>i</sub>     | Input currents        |                            | NA   | NA   | mA   |

| Б                  | May new a discinction | T <sub>CASE</sub> = -55°C  |      | 0.27 | W    |

| P <sub>DMAX</sub>  | Max power dissipation | $T_{CASE} = +125^{\circ}C$ |      | 0.27 | W    |

| T <sub>STG</sub>   | Storage temperature   |                            | -55  | +150 | °C   |

| TJ                 | Junction temperature  |                            |      | +150 | °C   |

| T <sub>LEADS</sub> | Lead temperature      | Max 5 sec. Soldering       |      | +270 | °C   |

Table 2-1.

Absolute Maximum Ratings

2.4.4.2 Recommended Condition of Use and Guaranteed Characteristics

• Guaranteed Characteristics (Table 2-5 and Table 2-8)

The characteristics associated to a specified measurement in the detail specification shall only be for inspection purposes.

Such characteristic defined in this specification is guaranteed only under the conditions and within the limits which are specified for the relevant measurement. Unless otherwise specified, this guarantee applies within all the recommended operating ranges specified below.

• Recommended conditions of use (Table 2-2)

To the correct operation of the device, the conditions of use shall be within the ranges specified below (see also above).

These conditions shall not be for inspection purposes.

Some recommended values may, however, be taken in other parts of this specification as detail conditions for an applicable test (Table 2-9).

Additional Electrical Characteristics (Table 2-9), see "Additional Electrical Characteristics" on page 30.

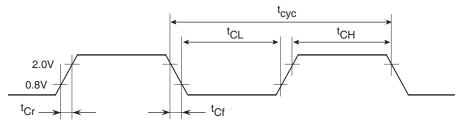

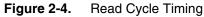

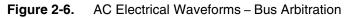

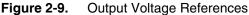

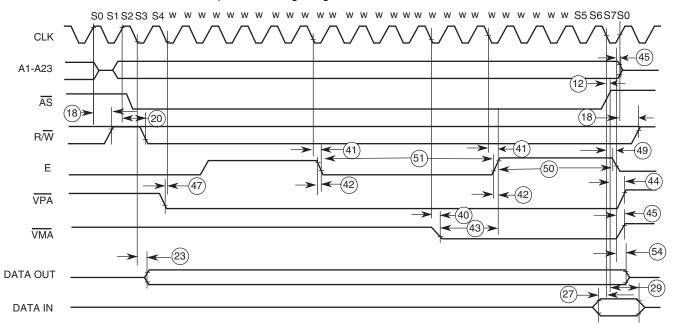

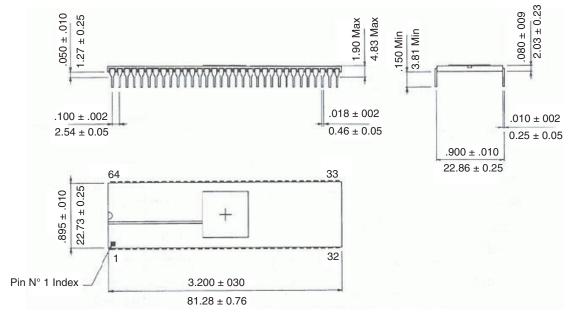

Figure 2-1. Clock Input Timing Diagram

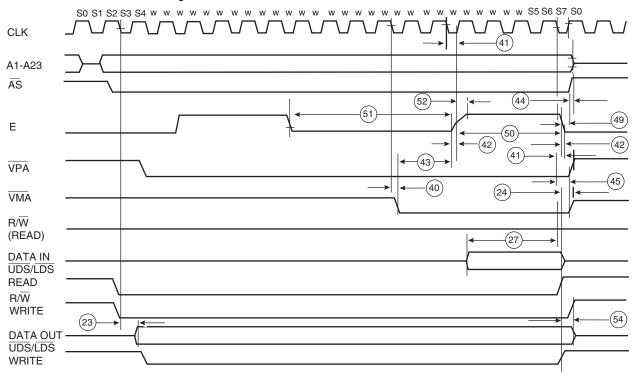

Note: Timing measurements are referenced to and from a low voltage of 0.8V and a high voltage of 2.0V, unless otherwise noted. The voltage swing through this range should start outside, and pass through, the range such that the rise of fall will be linear between 0.8V and 2.0V.

Unless otherwise stated, all voltages are referenced to the reference terminal (see Table 1-1).

#### Table 2-2. Recommended Condition of Use

|                    |                                                          |             | Operating Range |                 |      |  |  |

|--------------------|----------------------------------------------------------|-------------|-----------------|-----------------|------|--|--|

| Symbol             | Parameter                                                | Model       | Min             | Мах             | Unit |  |  |

| V <sub>CC</sub>    | Supply voltage                                           | All         | 4.5             | 5.5             | V    |  |  |

| V <sub>IL</sub>    | Low level input voltage                                  | All         | 0               | 0.8             | V    |  |  |

| V <sub>IH</sub>    | High level input voltage (see also "Package" on page 10) | All         | 2.0             | V <sub>CC</sub> | V    |  |  |

| T <sub>CASE</sub>  | Operating temperature                                    | All         | -55             | +125            | °C   |  |  |

| RL                 | Value of output load resistance                          | All         | (1)             |                 | Ω    |  |  |

| CL                 | Output loading capacitance                               | All         |                 | (1)             | pF   |  |  |

| t <sub>r(c)</sub>  | Clock rise time (see Figure 2-1)                         | All         |                 | 10              | ns   |  |  |

| t <sub>f(c)</sub>  | Clock fall time (see Figure 2-1)                         | All         |                 | 10              | ns   |  |  |

|                    |                                                          | TS68C000-8  | 4.0             | 8.0             | MHz  |  |  |

| f <sub>C</sub>     | Clock frequency (see Figure 2-1)                         | TS68C000-10 | 4.0             | 10.0            | MHz  |  |  |

|                    |                                                          | TS68C000-12 | 4.0             | 12.5            | MHz  |  |  |

|                    |                                                          | TS68C000-8  | 125             | 250             | ns   |  |  |

| t <sub>CYC</sub>   | Clock time (see Figure 2-1)                              | TS68C000-10 | 100             | 250             | ns   |  |  |

|                    |                                                          | TS68C000-12 | 80              | 250             | ns   |  |  |

|                    |                                                          | TS68C000-8  | 55              | 125             | ns   |  |  |

| t <sub>W(CL)</sub> | Clock pulse width low (see Figure 2-1)                   | TS68C000-10 | 45              | 125             | ns   |  |  |

|                    |                                                          | TS68C000-12 | 35              | 125             | ns   |  |  |

|                    |                                                          | TS68C000-8  | 55              | 125             | ns   |  |  |

| t <sub>W(CH)</sub> | Cycle pulse width high (see Figure 2-1)                  | TS68C000-10 | 45              | 125             | ns   |  |  |

|                    |                                                          | TS68C000-12 | 35              | 125             | ns   |  |  |

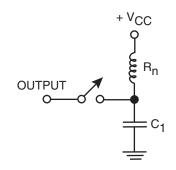

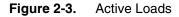

Note: 1. Load networks number 1 to 4 as specified in "Test Conditions Specific to the Device" on page 26 (Figure 2-2 and Figure 2-3) gives the maximum loading for the relevant output.

2.4.4.3 Special Recommended Conditions for CMOS Devices

#### 1. CMOS Latch-up

The CMOS cell is basically composed of two complementary transistors (a P-channel and an Nchannel), and, in the steady state, only one transistor is turned-on. The active P-channel transistor sources current when the output is a logic high and presents a high impedance when the output is a logic low. Thus the overall result is extremely low power consumption because there is no power loss through the active P.channel transistor. Also since only once transistor is determined by leakage currents.

Because the basic CMOS cell is composed of two complementary transistors, a virtual semiconductor controlled rectifier (SCR) may be formed when an input exceeds the supply voltage. The SCR that is formed by this high input causes the device to become "latched" in a mode that may result in excessive current drain and eventual destruction of the device. Although the device is Implemented with input protection diodes, care should be exercised to ensure that the maximum input voltages specification is not exceeded tram voltage transients; others may require no additional circuitry.

- 2. CMOS Applications

- The TS68C000 completely satisfies the input/output drive requirements of CMOS logic devices.

- The HCMOS TS68C000 provides an order of magnitude power dissipation reduction when compared to the HMOS TS68000. However, the TS68C000 does not offer a "power down" or "halt" mode. The minimum operating frequency of the TS68C000 is 4 MHz.

#### 2.4.5 Thermal Characteristics

| Package  | Symbol               | Parameter                              | Value | Unit |

|----------|----------------------|----------------------------------------|-------|------|

|          | $\theta_{JA}$        | Thermal resistance junction to ambient | 25    | °C/W |

| DIL 64   | $\theta_{JC}$        | Thermal resistance junction to case    | 6     | °C/W |

|          | $\theta_{JA}$        | Thermal resistance junction to ambient | 30    | °C/W |

| PGA 68   | $\theta_{JC}$        | Thermal resistance junction to case    | 6     | °C/W |

| 1.000.00 | $\theta_{JA}$        | Thermal resistance junction to ambient | 40    | °C/W |

| LCCC 68  | $\theta_{JC}$        | Thermal resistance junction to case    | 8     | °C/W |

|          | $\theta_{JA}$        | Thermal resistance junction to ambient | 40    | °C/W |

| CQFP 68  | $\theta_{\text{JC}}$ | Thermal resistance junction to case    | 10    | °C/W |

#### Table 2-3.Thermal Characteristics

#### 2.4.5.1 Power Considerations

The average chip-junction temperature, T<sub>J</sub> in °C can be obtained from:

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

T<sub>A</sub> = Ambient Temperature, °C

$\theta_{JA}$  = Package Thermal Resistance, Junction-to-Ambient, °C/W

$P_D = P_{INT} + P_{I/O}$

$P_{INT} = I_{CC} \times V_{CC}$ , Watts – Chip Internal Power

P<sub>I/O</sub> = Power Dissipation on Input and Output Pins – User Determined

For most applications  $P_{I/O} < P_{INT}$  and can be neglected.

An Approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K: (T_{J} + 273)$$

Solving equations (1) and (2) for K gives:

$$K = P_{D}. (T_{A} + 273) + \theta_{JA} \cdot P_{D}^{2}$$

where K is constant pertaining to the particular part K can be determined from the equation (3) by measuring PD (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$ .

(1)

(2)

(3)

The total thermal resistance of a package  $(\theta_{JA})$  can be separated into two components,  $\theta_{JC}$  and  $\theta_{CA}$ , representing the barrier to heat flow from the semiconductor junction to the package (case), surface  $(\theta_{JC})$  and from the case to the outside ambient  $(\theta_{CA})$ .

These terms are related by the equation:

$\theta_{JA} = \theta_{JC} + \theta_{CA}$

(4)

$\theta_{JA}$  is device related and cannot be influenced by the user. However,  $\theta_{CA}$  is user dependent and can be minimized by such thermal management techniques as heat sinks, ambient air cooling and thermal convection. Thus, good thermal management on the part of the user can significantly reduce  $\theta_{CA}$  so that  $\theta_{JA}$  approximately equals  $\theta_{JC}$ . Substitution of  $\theta_{JC}$  for  $\theta_{JA}$  in equation (1) will result in a lower semiconductor junction temperature.

#### 2.4.6 Mechanical and Environmental

The microcircuits shall meet all mechanical environmental requirements of MIL-STD-883 for class B devices.

#### 2.4.7 Marking

The document where are defined the marking are identified in the related reference documents. Each microcircuit is legible and permanently marked with the following information as minimum:

- Atmel Logo

- Manufacturer's Part Number

- Class B Identification

- Date-code of inspection lot

- ESD Identifier if Available

- Country of Manufacturing

#### 2.5 Quality Conformance Inspection

#### 2.5.1 DESC/MIL-STD-883

Is in accordance with MIL-PRF-38535 and method 5005 of MIL-STD-883. Group A and B inspections are performed on each production lot. Group C and D inspection are performed on a periodical basis.

#### 2.6 Electrical Characteristics

#### 2.6.1 General Requirements

All static and dynamic electrical characteristics specified for inspection purposes and the relevant measurements conditions are given below:

- Table 2-4: Static Electrical Characteristics for all electrical variants.

- Table 2-5, Table 2-6, Table 2-7 and Table 2-8: Dynamic electrical characteristics for 8 MHz, 10 MHz and 12.5 MHz.

For static characteristics (Table 2-4), test methods refer to IEC 748-2 method number, where existing.

For dynamic characteristics, test methods refer to clause "Test Conditions Specific to the Device" on page 26 of this specification (Table 2-5, Table 2-6, Table 2-7 and Table 2-8).

Indication of "min" or "max" in the column "test temperature" means minimum or maximum operating temperatures as defined in sub-clause "Recommended Condition of Use and Guaranteed Characteristics" on page 11 here above.

#### Table 2-4. Static Characteristics

| $V_{00} = 5.0 V_{00} \pm 100 V_{00}$ | : 10%: GND = 0 | $V_{DC}$ : TC = | -55/+125°C | and -40°C/+85°C |

|--------------------------------------|----------------|-----------------|------------|-----------------|

|                                      |                | · DC, · · •     |            |                 |

|                |                                |                                                                                  | Ref            |                                                                                                    |                     |            | Limits                 |      |

|----------------|--------------------------------|----------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------|---------------------|------------|------------------------|------|

| Test<br>Number | Symbol                         | Parameter                                                                        | Number<br>(**) | Test<br>Conditions                                                                                 | Test<br>Temperature | Min<br>(*) | Max<br>(*)             | Unit |

| 1              | I <sub>cc</sub>                | Supply current                                                                   | 41             | $V_{CC} = 5.5V$<br>$F_{C} = 8 \text{ MHz}$<br>$F_{C} = 10 \text{ MHz}$<br>$F_{C} = 12 \text{ MHz}$ | All                 |            | 42<br>45<br>50         | mA   |

| 2              | V <sub>OL</sub> <sup>(1)</sup> | Low level output<br>voltage for: A1 to A23<br>FC0 to FC2; BG                     | 37             | V <sub>CC</sub> = 4.5V<br>I <sub>OL</sub> = 3.2 mA                                                 | 25°C<br>max<br>min  |            | 0.5                    | v    |

| 3              | V <sub>OL</sub> <sup>(2)</sup> | Low level output<br>voltage for:<br>HALT                                         | 37             | $V_{CC} = 4.5V$<br>$I_{OL} = 1.6 \text{ mA}$                                                       | 25°C<br>max<br>min  |            | 0.5                    | v    |

| 4              | V <sub>OL</sub> <sup>(3)</sup> | Low level output<br>voltage for:<br>AS; R/W:<br>D0 to D15 UDS;<br>LDS; VMA and E | 37             | V <sub>CC</sub> = 4.5V<br>I <sub>OL</sub> = 5.3 mA                                                 | 25°C<br>max<br>min  |            | 0.5                    | v    |

| 5              | V <sub>OL</sub> <sup>(4)</sup> | Low level output<br>voltage for:<br>RESET                                        | 37             | V <sub>CC</sub> = 4.5V<br>I <sub>OL</sub> = 5.0 mA                                                 | 25°C<br>max<br>min  |            | 0.5                    | v    |

| 6              | V <sub>OH</sub>                | High level output voltage for all outputs                                        | 37             | V <sub>CC</sub> = 4.5V<br>I <sub>OH</sub> = -400 μA                                                | 25°C<br>max<br>min  | 2.4        | V <sub>CC</sub> – 0.75 | v    |

| 7              | I <sub>IH</sub> (1)            | High level input current<br>for all inputs excepted<br>HALT and RESET            | 38             | $V_{CC} = 5.5V$<br>$V_I = 5.5V$                                                                    | 25°C<br>max<br>min  |            | 2.5                    | μA   |

| 8              | ا <sub>ال</sub> (1)            | Low level input current<br>for all inputs excepted<br>HALT and RESET             | 38             | $V_{CC} = 5.5V$<br>$V_1 = 0V$                                                                      | 25°C<br>max<br>min  | -2.5       |                        | μA   |

| 9              | I <sub>IH</sub> (2)            | High level input<br>current for:<br>HALT and RESET                               | 38             | V <sub>CC</sub> = 5.5V<br>V <sub>I</sub> = 5.5V                                                    | 25°C<br>max<br>min  |            | 20                     | μA   |

| 10             | I <sub>IL</sub> <sup>(2)</sup> | Low level input<br>current for:<br>HALT and RESET                                | 38             | $V_{CC} = 5.5V$<br>$V_1 = 0V$                                                                      | 25°C<br>max<br>min  | -20        |                        | μA   |

Table 2-4.Static Characteristics (Continued) $V_{CC} = 5.0V V_{DC} \pm 10\%$ ; GND = 0  $V_{DC}$ ; Tc = -55/+125°C and -40°C/+85°C

|                |                   |                                                | Ref            |                                     |                     |            | Limits         |      |

|----------------|-------------------|------------------------------------------------|----------------|-------------------------------------|---------------------|------------|----------------|------|

| Test<br>Number | Symbol            | Parameter                                      | Number<br>(**) | Test<br>Conditions                  | Test<br>Temperature | Min<br>(*) | Max<br>(*)     | Unit |

|                |                   |                                                |                | $V_{CC} = 5.5V$                     | 25°C                |            |                |      |

| 11             | I <sub>OHZ</sub>  | High level output<br>3-state leakage current   |                |                                     | max                 |            | 20             | μΑ   |

|                |                   | o state leakage current                        |                | $V_{OH} = 2.4V$                     | min                 |            | 20<br>0<br>0.8 |      |

|                |                   |                                                |                | $V_{CC} = 5.5V$                     | 25°C                |            |                |      |

| 12             | I <sub>OLZ</sub>  | Low level output<br>3-state leakage current    |                |                                     | max                 |            | 20             | μΑ   |

|                |                   | 5-State leakage current                        |                | $V_{OL} = 0.4V$                     | min                 |            | .0             |      |

|                |                   |                                                |                | $V_{CC} = 4.5V$                     | 25°C                |            |                |      |

| 13             | V <sub>IH</sub>   | High level input voltage for all inputs        |                |                                     | max                 | 2.0        |                | V    |

|                |                   | voltage for an inputs                          |                | $V_{CC} = 5.5V$                     | min                 |            | 0.8            |      |

|                |                   |                                                |                | $V_{CC} = 4.5V$                     | 25°C                |            | 0.8            | V    |

| 14             | V <sub>IL</sub>   | Low level input<br>voltage for all inputs      |                |                                     | max                 |            | 0.8            | V    |

|                |                   | voltage for an inputs                          |                | $V_{CC} = 5.5V$                     | min                 |            | 0.8            | V    |

|                |                   |                                                |                | Reverse                             | 25°C                |            | 25             | pF   |

| 14A            | C <sub>IN</sub>   | Input capacitance<br>(all inputs)              | 11             | voltage = 0V                        | max                 |            | NA             | pF   |

|                |                   |                                                |                | f = 1.0 MHz                         | min                 |            | NA             | pF   |

|                |                   |                                                |                | Reverse                             | 25°C                |            | 20             | pF   |

| 14B            | C <sub>OUT</sub>  | Output capacitance<br>(all inputs)             | 11             | voltage = 0V                        | max                 |            | NA             | pF   |

|                |                   |                                                |                | f = 1.0 MHz                         | min                 |            | NA             | pF   |

| 14C            | V <sub>TEST</sub> | Internal protection<br>Transient energy rating |                | See note <sup>(9)</sup><br>5 cycles | 25°C                | -500       | +500           | V    |

Note: \* Algebraic values

\*\* Measurement method: see "General Requirements" on page 14 and "Test Conditions Specific to the Device" on page 26. Referred notes are given on page 25.

**Table 2-5.**Dynamic Characteristics – TS68C000-8

|                |                        |                                                    | Figure<br>Number<br>(**) |                                                                     | Test<br>Temperature | Limits             |            |      |

|----------------|------------------------|----------------------------------------------------|--------------------------|---------------------------------------------------------------------|---------------------|--------------------|------------|------|

| Test<br>Number | Symbol                 | Parameter                                          |                          | Test<br>Conditions                                                  |                     | Min<br>(*)         | Max<br>(*) | Unit |

|                |                        |                                                    |                          | See "Input and<br>Output Signals<br>for Dynamic                     | 25°C                |                    |            |      |

|                |                        |                                                    |                          |                                                                     | max                 | 1                  |            |      |

| 27             | t <sub>SU</sub> (DICL) | Set-up time<br>Data-in to clock low <sup>(1)</sup> | 10 – 11                  | Measurements"<br>on page 29<br>(a) to (c)<br>f <sub>C</sub> = 8 MHz | min                 | 20 <sup>(10)</sup> |            | ns   |

| Table 2-5. | Dynamic Characteristics – TS68C000-8 (Continued)                                    |

|------------|-------------------------------------------------------------------------------------|

|            | $V_{co} = 5.0 V_{co} + 10\%$ ; GND = 0 $V_{co}$ ; Tc = -55/+125°C and Tc = -40°C/+8 |

|                |                             |                                                   | Figure         |                    |                     | Lin                | nits              |      |

|----------------|-----------------------------|---------------------------------------------------|----------------|--------------------|---------------------|--------------------|-------------------|------|

| Test<br>Number | Symbol                      | Parameter                                         | Number<br>(**) | Test<br>Conditions | Test<br>Temperature | Min<br>(*)         | Max<br>(*)        | Unit |

|                |                             | Set-up time                                       |                |                    | 25°C                |                    |                   |      |

| 47             | t <sub>SU</sub><br>(SDTCL)  | DTACK low to clock                                | 10 – 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                | (00102)                     | low <sup>(1)</sup>                                |                |                    | min                 |                    |                   |      |

|                |                             |                                                   |                |                    | 25°C                |                    |                   |      |

| 47             | t <sub>SU</sub><br>(SBRCL)  | Set-up time<br>BR low to clock low <sup>(1)</sup> | 10 – 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                | (SBROL)                     | BR IOW TO CIOCK IOW                               |                |                    | min                 | +                  |                   |      |

|                |                             | Set-up time                                       |                |                    | 25°C                |                    |                   |      |

| 47             | t <sub>SU</sub><br>(SBGCL)  | BGACK low to clock                                | 10 – 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                | (SDGUL)                     | low <sup>(1)</sup>                                |                |                    | min                 | -                  |                   |      |

|                |                             | Sat un tima                                       |                |                    | 25°C                |                    |                   |      |

| 47             | t <sub>SU</sub>             | Set-up time<br>VPA low to clock low               | 10 – 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                | (SVPACL)                    | (1)                                               |                |                    | min                 |                    |                   |      |

|                |                             |                                                   |                |                    | 25°C                |                    |                   |      |

| 47             | 47 (SBERCL)                 | Set-up time BERR                                  | 10 – 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                |                             | low to clock low <sup>(1)</sup>                   |                |                    | min                 | -                  |                   |      |

|                |                             |                                                   |                |                    | 25°C                |                    | 125               | ns   |

| 2              | t <sub>w</sub>              | Clock width low                                   | 10 – 11        | ldem test 27       | max                 | 55 <sup>(10)</sup> |                   |      |

|                | (CL)                        |                                                   |                |                    | min                 |                    |                   |      |

|                |                             |                                                   |                |                    | 25°C                |                    |                   |      |

| 3              | t <sub>w</sub>              | Clock width high                                  | 10 – 11        | ldem test 27       | max                 | 55                 | 125               | ns   |

| C              | (CH)                        | crook main ngh                                    | 10 11          |                    | min                 |                    | 120               | 110  |

|                |                             |                                                   |                |                    | 25°C                |                    |                   |      |

| 6A             | t <sub>PLH</sub>            | Propagation time                                  | 10 – 11        | Idem<br>test 27    | max                 | -                  | 70                | ns   |

| 0/1            | t <sub>PHL</sub><br>(CHFCV) | clock high to FC valid                            |                | Load: 3            | min                 | -                  | 10                | ns   |

|                |                             |                                                   |                |                    | 25°C                |                    |                   |      |

| 9              | t <sub>PHL</sub>            | Propagation time                                  | 10 – 11        | Idem<br>test 27    | max                 |                    | 60 <sup>(3)</sup> |      |

| 9              | (CHSLX)                     | clock high to AS low                              | 10 - 11        | Load: 4            |                     |                    | 00.7              |      |

|                |                             |                                                   |                |                    | min                 |                    |                   |      |

| 0              | t <sub>PHL</sub>            | Propagation time                                  | 10 – 11        | Idem<br>test 27    | 25°C                | -                  | 60 <sup>(3)</sup> |      |

| 9              | (CHSL)                      | CLK high to LDS,<br>UDS low                       | 10 - 11        | Load: 4            | max                 | -                  | 00                | ns   |

|                |                             |                                                   |                |                    | min                 |                    |                   |      |

| 10             | t <sub>енн</sub>            | Propagation time                                  | 10 – 11        | Idem               | 25°C                | -                  | 70 <sup>(3)</sup> |      |

| 12             | τ <sub>ΡLΗ</sub><br>(CLSH)  |                                                   |                | test 27<br>Load: 4 | max                 | -                  | 70(%)             | ns   |

Table 2-5.Dynamic Characteristics – TS68C000-8 (Continued) $V_{CC} = 5.0 V_{DC} \pm 10\%$ ; GND = 0  $V_{DC}$ ; Tc = -55/+125°C and Tc = -40°C/+85°C

|                |                             |                                          | Figure                |                    |                     | Lin        | nits              |      |

|----------------|-----------------------------|------------------------------------------|-----------------------|--------------------|---------------------|------------|-------------------|------|

| Test<br>Number | Symbol                      | Parameter                                | Number<br>(**)        | Test<br>Conditions | Test<br>Temperature | Min<br>(*) | Max<br>(*)        | Unit |

|                |                             | Propagation time                         |                       | Idem               | 25°C                |            |                   |      |

| 12             | t <sub>PLH</sub><br>(CLSH)  | CLK low to LDS, UDS                      | 10 – 11               | test 27            | max                 |            | 70 <sup>(3)</sup> | ns   |

|                |                             | high                                     |                       | Load: 4            | min                 |            |                   |      |

|                | _                           |                                          |                       | ldem               | 25°C                |            |                   |      |

| 18             | t <sub>PLH</sub><br>(CHRHX) | Propagation time<br>CLK high to R/W high | 10 – 11               | test 27            | max                 |            | 70 <sup>(3)</sup> | ns   |

|                | · · · · ·                   |                                          |                       | Load: 4            | min                 |            |                   |      |

|                |                             |                                          | Ide                   | ldem               | 25°C                |            |                   |      |

| 20             | t <sub>PHL</sub><br>(CHRL)  | Propagation time<br>CLK high to R/W low  | 10 – 11               | test 27            | max                 |            | 70 <sup>(3)</sup> | ns   |

|                | . ,                         |                                          |                       | Load: 4            | min                 |            |                   |      |

|                | t <sub>PZL</sub>            | Propagation time                         |                       | ldem               | 25°C                |            |                   |      |

| 23             | t <sub>PZH</sub>            | CLK low to Data-out                      | 10 – 11               | test 27            | max                 |            | 70 <sup>(3)</sup> | ns   |

|                | (CLDO)                      | valid                                    |                       | Load: 4            | min                 |            |                   |      |

|                | t <sub>PZL</sub>            | Propagation time                         |                       | ldem               | 25°C                |            |                   |      |

| 6              | 6 t <sub>PZH</sub> CL       | CLK low to Address                       | 10 – 11               |                    | max                 |            | 70                | ns   |

|                | (CLAV)                      | valid                                    |                       | Load: 3            | min                 |            |                   |      |

|                |                             |                                          |                       |                    | 25°C                |            |                   |      |

| 32             | t <sub>HRRF</sub>           | RESET/HALT input<br>transition time      | <sup>ut</sup> 10 – 11 | Idem<br>test 27    | max                 |            | 200               | ns   |

|                |                             |                                          |                       |                    | min                 |            |                   |      |

|                |                             |                                          |                       | ldem               | 25°C                |            |                   |      |

| 33             | t <sub>PHL</sub><br>(CHGL)  | Propagation time<br>CLK high to BG low   | 12                    | test 27            | max                 |            | 70                | ns   |

|                |                             |                                          |                       | Load: 3            | min                 |            |                   |      |

|                | _                           |                                          |                       | ldem               | 25°C                |            |                   |      |

| 34             | t <sub>PLH</sub><br>(CHGH)  | Propagation time<br>CLK high to BG high  | 12                    | test 27            | max                 |            | 70                | ns   |

|                | , ,                         |                                          |                       | Load: 3            | min                 |            |                   |      |

|                |                             |                                          |                       | ldem               | 25°C                |            |                   |      |

| 40             | t <sub>PHL</sub><br>(CLVM)  | Propagation time<br>CLK low to VMA low   | 13                    | test 27            | max                 |            | 70                | ns   |

|                | . ,                         |                                          |                       | Load: 4            | min                 |            |                   |      |

|                |                             |                                          |                       | ldem               | 25°C                |            |                   |      |

| 41             | t <sub>PHL</sub><br>(CLE)   | Propagation time<br>CLK low to E low     | 13                    | test 27            | max                 |            | 70                | ns   |

|                | . ,                         |                                          |                       | Load: 4            | min                 |            |                   |      |

|                |                             |                                          |                       | Idem               | 25°C                |            |                   |      |

| 8              | t <sub>h</sub><br>(SHAZ)    | Hold time CLK high to Address            | 10 – 11               | test 27<br>Load: 3 | max                 | 0          |                   | ns   |

|                |                             |                                             | Figure         |                    |                     | Lin               | nits       |      |

|----------------|-----------------------------|---------------------------------------------|----------------|--------------------|---------------------|-------------------|------------|------|

| Test<br>Number | Symbol                      | Parameter                                   | Number<br>(**) | Test<br>Conditions | Test<br>Temperature | Min<br>(*)        | Max<br>(*) | Unit |

|                |                             | Set-up time                                 |                | Idem               | 25°C                |                   |            |      |

| 11             | t <sub>SU</sub><br>(AVSL)   | Address valid to                            | 10 – 11        | test 27            | max                 | 30 <sup>(4)</sup> |            | ns   |

|                | ()                          | AS, LDS, UDS low                            |                | Load: 4            | min                 |                   |            |      |

|                |                             | Propagation time                            |                | ldem               | 25°C                |                   | 3.5        | CLKS |

| 35             | t <sub>PHL</sub><br>(BRLGL) | BR low to                                   | 12             | test 27            | max                 | 1.5               |            | (2)  |

| ()             | BG low                      |                                             | Load: 3        | min                |                     | +90               | ns         |      |

|                |                             | Propagation time<br>BGACK low to<br>BG high | 12             | ldem               | 25°C                | 1.5               | 3.5        | CLKS |

| 37             | t <sub>PLH</sub><br>(GALEH) |                                             |                | test 27            | max                 |                   |            |      |

|                | (0                          |                                             |                | Load: 3            | min                 |                   | +90        | ns   |

|                |                             | Set-up time                                 |                | ldem<br>test 27    | 25°C                |                   |            |      |

| 48             | t <sub>SU</sub><br>(BELDAL) | BERR low to                                 | 11             |                    | max                 | 20 <sup>(5)</sup> | _          | ns   |

|                | ()                          | DTACK low                                   |                |                    | min                 |                   |            |      |

|                |                             | Set-up time                                 |                |                    | 25°C                |                   |            |      |

| 48             | t <sub>SU</sub><br>(BELDAL) | BERR low to                                 | 10 – 11        | Idem<br>test 27    | max                 | 20 <sup>(5)</sup> | _          | ns   |

|                | ()                          | DTACK low                                   |                |                    | min                 |                   |            |      |

|                |                             | Hold time                                   |                | Idem               | 25°C                |                   |            |      |

| 26             | t <sub>h</sub><br>(DOSL)    | Data-out valid to                           | 11             | test 27            | max                 | 30 <sup>(4)</sup> | —          | ns   |

|                | (_ ) • • •                  | LDS, UDS low                                |                | Load: 4            | min                 |                   |            |      |

Table 2-5.Dynamic Characteristics - TS68C000-8 (Continued) $V_{CC} = 5.0 V_{DC} \pm 10\%$ ; GND = 0  $V_{DC}$ ; Tc = -55/+125°C and Tc = -40°C/+85°C

Note: \* Algebraic values

\*\* Measurement method: see "General Requirements" on page 14 and "Test Conditions Specific to the Device" on page 26 Referred notes are given on page 25.

|                         |                            |                                                         | Figure         |                                                                                                             |                     | Limits             |            |      |

|-------------------------|----------------------------|---------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------|---------------------|--------------------|------------|------|

| Test<br>Number          | Symbol                     | Parameter                                               | Number<br>(**) | Test<br>Conditions                                                                                          | Test<br>Temperature | Min<br>(*)         | Max<br>(*) | Unit |

|                         |                            |                                                         |                | See "Input and<br>Output Signals<br>for Dynamic<br>Measurements"<br>on page 29<br>(a) to (c)<br>fc = 10 MHz | 25°C                |                    |            |      |

| 27 t <sub>su</sub> (DIC |                            | Set-up time<br>Data-in to clock low <sup>(1)</sup>      | 10 – 11        |                                                                                                             | max                 |                    |            |      |

|                         | t <sub>SU</sub> (DICL)     |                                                         |                |                                                                                                             | min                 | 20 <sup>(10)</sup> |            | ns   |

|                         |                            | Set-up time<br>DTACK low to clock<br>low <sup>(1)</sup> |                |                                                                                                             | 25°C                |                    |            |      |

| 47                      | t <sub>SU</sub><br>(SDTCL) |                                                         | 10 – 11        | ldem test 27                                                                                                | max                 | 20 <sup>(10)</sup> |            | ns   |

|                         | (02102)                    |                                                         |                |                                                                                                             | min                 |                    |            |      |

**Table 2-6.**Dynamic Characteristics – TS68C000-10

| Table 2-6. | Dynamic Characteristics – TS68C000-10 (Continued) |

|------------|---------------------------------------------------|

|------------|---------------------------------------------------|

|                  |                                           |                                                     | Figure         |                    |                     | Lin                | nits              |      |

|------------------|-------------------------------------------|-----------------------------------------------------|----------------|--------------------|---------------------|--------------------|-------------------|------|

| Test<br>Number   | Symbol                                    | Parameter                                           | Number<br>(**) | Test<br>Conditions | Test<br>Temperature | Min<br>(*)         | Max<br>(*)        | Unit |

|                  |                                           |                                                     |                |                    | 25°C                |                    |                   |      |

| 47               | t <sub>SU</sub><br>(SBRCL)                | Set-up time<br>BR low to clock low <sup>(1)</sup>   | 10 – 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                  | ()                                        | Bit low to clock low                                |                |                    | min                 |                    |                   |      |

|                  |                                           | Set-up time                                         |                |                    | 25°C                |                    |                   |      |

| 47               | t <sub>SU</sub><br>(SBGCL)                | BGACK low to clock                                  | 10 – 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                  | · · · ·                                   | low <sup>(1)</sup>                                  |                |                    | min                 |                    |                   |      |

|                  |                                           | Set-up time                                         |                |                    | 25°C                | _                  |                   |      |

| 47               | t <sub>su</sub><br>(SVPACL)               | VPA low to clock low                                | 10 – 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                  |                                           |                                                     |                |                    | min                 |                    |                   |      |

|                  |                                           | 0 · · · · <u>2522</u>                               |                |                    | 25°C                | _                  |                   |      |

| 47               | 47 <sup>t</sup> <sub>SU</sub><br>(SBERCL) | Set-up time BERR<br>low to clock low <sup>(1)</sup> | 10 — 11        | ldem test 27       | max                 | 20 <sup>(10)</sup> |                   | ns   |

|                  | · · · · ·                                 |                                                     |                |                    | min                 |                    |                   |      |

|                  |                                           |                                                     |                |                    | 25°C                | _                  |                   |      |

| 2 t <sub>w</sub> | (CL)                                      | Clock width low                                     | 10 — 11        | ldem test 27       | max                 | 45                 | 125               | ns   |

|                  | . ,                                       |                                                     |                |                    | min                 |                    |                   |      |

|                  | +                                         |                                                     |                | ldem test 27       | 25°C                | _                  | 125               |      |

| 3                | t <sub>w</sub><br>(CH)                    |                                                     | 10 – 11        |                    | max                 | 45                 |                   | ns   |

|                  | (0.1)                                     |                                                     |                |                    | min                 |                    |                   |      |

|                  | t <sub>PLH</sub>                          | <b>_</b>                                            |                | ldem               | 25°C                | _                  |                   |      |

| 6A               | t <sub>PHL</sub>                          | Propagation time<br>clock high to FC valid          | 10 — 11        | test 27<br>Load: 3 | max                 |                    | 60                | ns   |

|                  | (CHFCV)                                   |                                                     |                |                    | min                 |                    |                   |      |

|                  |                                           | <b>_</b>                                            |                | ldem               | 25°C                | _                  |                   |      |

| 9                | t <sub>PHL</sub><br>(CHSLX)               | Propagation time<br>clock high to AS low            | 10 — 11        | test 27            | max                 | _                  | 55 <sup>(3)</sup> | ns   |

|                  |                                           |                                                     |                | Load: 4            | min                 |                    |                   |      |

|                  |                                           | Propagation time                                    |                | ldem               | 25°C                |                    |                   |      |

| 9                | t <sub>PHL</sub><br>(CHSL)                | CLK high to LDS,                                    | 10 — 11        | test 27            | max                 | _                  | 55 <sup>(3)</sup> | ns   |

|                  | . ,                                       | UDS low                                             |                | Load: 4            | min                 |                    |                   |      |

|                  |                                           |                                                     |                | ldem               | 25°C                |                    |                   |      |

| 12               | t <sub>PLH</sub><br>(CLSH)                | Propagation time<br>CLK low to AS high              | 10 — 11        | test 27            | max                 |                    | 55 <sup>(3)</sup> | ns   |

|                  | ()                                        |                                                     |                | Load: 4            | min                 |                    |                   |      |

|                  |                                           | Propagation time                                    |                | Idem               | 25°C                |                    |                   | ns   |

| 12               | t <sub>PLH</sub><br>(CLSH)                | CLK low to LDS LIDS                                 | 10 — 11        | test 27            | max                 | ļ                  | 55 <sup>(3)</sup> |      |

|                  | (                                         |                                                     |                | Load: 4            | min                 |                    |                   |      |

| Table 2-6. | Dynamic Characteristics - TS68C000-10 (Continued) |

|------------|---------------------------------------------------|

|            |                                                   |

|                |                                         |                                          | Figure         |                    |                     | Lin               | nits              |      |

|----------------|-----------------------------------------|------------------------------------------|----------------|--------------------|---------------------|-------------------|-------------------|------|

| Test<br>Number | Symbol                                  | Parameter                                | Number<br>(**) | Test<br>Conditions | Test<br>Temperature | Min<br>(*)        | Max<br>(*)        | Unit |

|                |                                         |                                          |                | Idem               | 25°C                |                   |                   |      |

| 18             | t <sub>PLH</sub><br>(CHRHX)             | Propagation time<br>CLK high to R/W high | 10 — 11        | test 27            | max                 |                   | 60 <sup>(3)</sup> | ns   |

|                | (0                                      | • <u>-</u>                               |                | Load: 4            | min                 |                   |                   |      |

|                |                                         |                                          |                | Idem               | 25°C                |                   |                   |      |

| 20             | t <sub>PHL</sub><br>(CHRL)              | Propagation time<br>CLK high to R/W low  | 10 – 11        | test 27            | max                 |                   | 60 <sup>(3)</sup> | ns   |

|                |                                         | 3                                        |                | Load: 4            | min                 |                   |                   |      |

|                | t <sub>PZL</sub>                        | Propagation time                         |                | Idem               | 25°C                |                   |                   |      |

| 23             | t <sub>PZH</sub>                        | CLK low to Data-out                      | 10 – 11        | test 27            | max                 |                   | 55 <sup>(3)</sup> | ns   |

|                | (CLDO)                                  | valid                                    |                | Load: 4            | min                 |                   |                   |      |

|                | t <sub>PZL</sub>                        | Propagation time                         |                | Idem               | 25°C                |                   |                   |      |

| 6              | t <sub>PZH</sub>                        | CLK low to Address                       | 10 — 11        | test 27            | max                 |                   | 60                | ns   |

|                | (CLAV)                                  | valid                                    |                | Load: 4            | min                 |                   |                   |      |

|                |                                         |                                          |                |                    | 25°C                |                   |                   |      |

| 32 (           | t <sub>HRRF</sub><br>(CHGL)             | RESET/HALT input<br>transition time      | 10 – 11        | Idem<br>test 27    | max                 |                   | 200               | ns   |

|                | ( )                                     |                                          |                |                    | min                 |                   |                   |      |

|                |                                         | HL Propagation time 12 test 27 m         | 25°C           |                    |                     |                   |                   |      |

| 33             | t <sub>PHL</sub><br>(CHGL)              |                                          | 12             | test 27            | max                 |                   | 60                | ns   |

|                | ()                                      | ege _ ee.                                |                | Load: 3            | min                 |                   |                   |      |

|                |                                         |                                          |                | Idem               | 25°C                |                   |                   |      |

| 34             | t <sub>PLH</sub><br>(CHGH)              | Propagation time<br>CLK high to BG high  | 12             | test 27            | max                 |                   | 60                | ns   |

|                | (0.1.0)                                 | ege _ eg                                 |                | Load: 3            | min                 |                   |                   |      |

|                |                                         |                                          |                | Idem               | 25°C                |                   |                   |      |

| 40             | t <sub>PHL</sub><br>(CLVM)              | Propagation time<br>CLK low to VMA low   | 13             | test 27            | max                 |                   | 70                | ns   |

|                | (,                                      |                                          |                | Load: 4            | min                 |                   |                   |      |

|                |                                         |                                          |                | Idem               | 25°C                |                   |                   |      |

| 41             | t <sub>PHL</sub><br>(CLE)               | Propagation time<br>CLK low to E low     | 13             | test 27            | max                 |                   | 55                | ns   |

|                | ()                                      |                                          |                | Load: 4            | min                 |                   |                   |      |

|                |                                         |                                          |                | Idem               | 25°C                |                   |                   |      |

| 8              | t <sub>H</sub><br>(SHAZ)                | Hold time CLK high<br>to Address         | 10 – 11        | test 27            | max                 | 0                 |                   | ns   |

|                | (0. " (-)                               |                                          |                | Load: 3            | min                 |                   |                   |      |

|                |                                         | Set-up time                              |                | Idem               | 25°C                |                   |                   |      |

| 11             | t <sub>SU</sub><br>(AVSL)               | Address valid to                         | 10 – 11        | test 27            | max                 | 20 <sup>(4)</sup> |                   | ns   |

|                | (,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | AS, LDS, UDS low                         |                | Load: 4            | min                 |                   |                   |      |

|                |                             |                            | Figure         |                     |                     | Lin               | nits       |      |

|----------------|-----------------------------|----------------------------|----------------|---------------------|---------------------|-------------------|------------|------|

| Test<br>Number | Symbol                      | Parameter                  | Number<br>(**) | Test<br>Conditions  | Test<br>Temperature | Min<br>(*)        | Max<br>(*) | Unit |